|

|

|

|

| |

Introduction

Hello all, I am back on the projects again after the traumas of moving three households into one house. Now I can perhaps have a bit of time on the workbench. The windows all open, the mice are dead and the bathrooms have been re-built. Now I want to do a little work with synthesizers. There are already a couple of synthesized projects on the homepage but I intend to do a lot more. Perhaps this is the time to do a little explaining and to introduce a couple of basic techniques and terms.

So What Is A Frequency Synthesizer?

The answer to that is easy, it is a programable frequency multiplier, usually using digital logic integrated circuits. The synthesizer is aranged to multiply a reference frequency by a programable amount to achieve just about any frequency you want. If, for example you had a reference frequency of, say, 1KHz and a "programable multiplier" then you could program the multiplier to give you 1KHz (X1), 3KHz (X3), 1.025MHz (X1025), 98.325MHz (X98325) or any other frequency you want. Sounds easy? Actually, it is so easy, once you understand some of the basics. So let us start off by building a simple synthesizer that cover 3KHz to 4000KHz (4MHz).

Basic PLL Operation

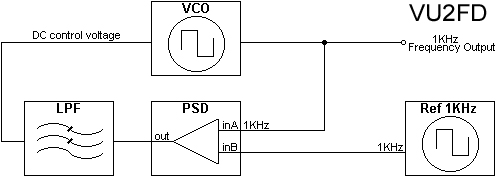

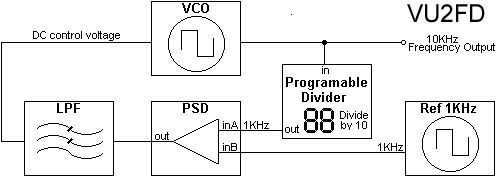

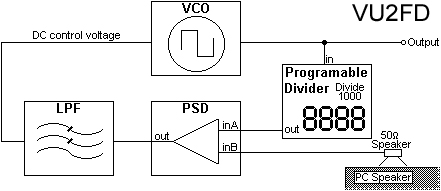

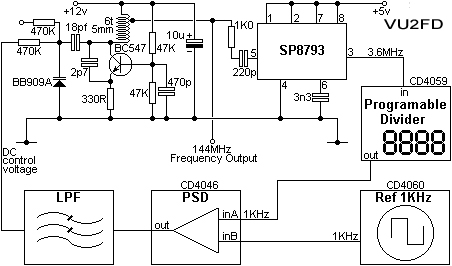

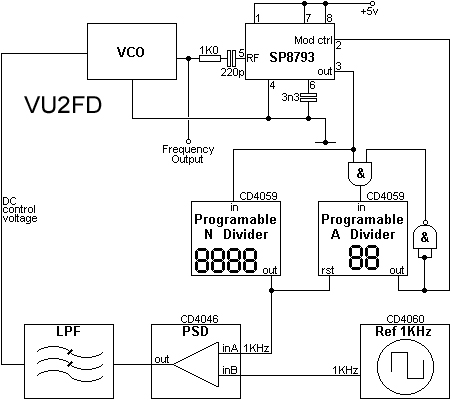

A Phase Locked Loop (PLL) consists of a Voltage Controlled Oscillator (VCO), the output frequency of which is monitored and controlled. An error voltage steers the VCO and brings it back onto the correct frequency. The error voltage is generated by a Phase Sensitive Detector (PSD) which compares the VCO frequency with a reference frequency. Consider the following block diagram: